4 月 19 日消息,SK 海力士宣布和臺積電簽署諒解備忘錄(MOU),推進 HBM4 研發和下一代封裝技術,目標在 2026 年投產 HBM4。

根據雙方簽署的諒解備忘錄,兩家公司初期目標是改善 HBM 封裝內最底層基礎裸片(Base Die)的性能。

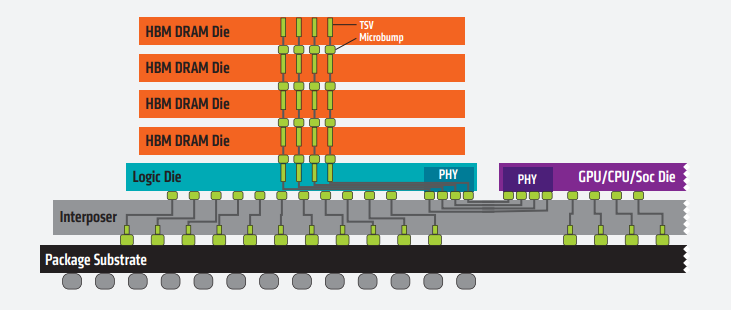

IT之家注:HBM 是將多個 DRAM 裸片(Core Die)堆疊在基礎裸片上,并通過 TSV 技術進行垂直連接而成,基礎裸片也連接至 GPU,在 HBM 中扮演非常重要的角色。

包括 HBM3E(第五代 HBM 產品)在內,SK 海力士旗下 HBM 產品的基礎裸片此前均采用自家工藝制造,而從 HMB4(第六代 HBM 產品)開始,該公司將采用臺積電的先進邏輯(Logic)工藝。

消息稱雙方將會展開緊密合作,嘗試使用臺積電的 CoWoS 技術封裝 SK 海力士的 HBM 產品,從而在性能和功效等方面,進一步滿足客戶的定制化(Customized)HBM 產品需求。

SK 海力士今年 2 月還制定了 One Team 戰略,通過臺積電建立 AI 半導體同盟,進一步鞏固在 HBM 領域的優勢。

▲ HBM 內存結構示意圖,圖源 AMD 官網

此外,未來 AI 半導體將從 HBM 時代的 2.5D 封裝走向 3D 堆疊邏輯芯片和存儲芯片的新型高級封裝。存儲企業同芯片代工 + 高級封裝企業的合作有利于相關研發推進。